A lot of people have been asking about Rosepoint, the Intel Atom plus digital radio. The most asked question is “how big is it”?

A lot of people have been asking about Rosepoint, the Intel Atom plus digital radio. The most asked question is “how big is it”?

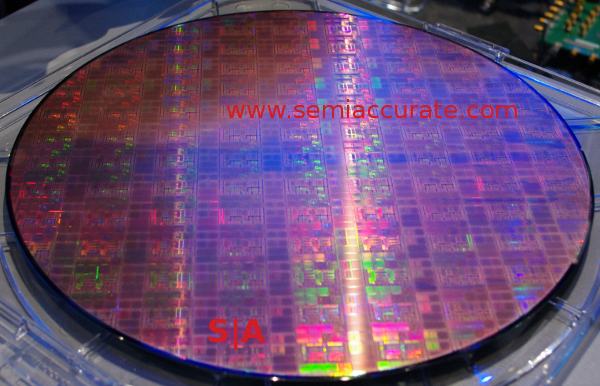

The answer isn’t that easy, especially since Intel showed the wafer from a distance, and then pulled it away as soon as the post keynote picture melee began. Luckily, it was after SemiAccurate managed to grab 2.5 pictures of the wafer. The last .5 is partially obscured by the hand yanking it away, and quite blurry. The full wafer looks like this.

The wafer in question

Non-instrumented measurements of the die size, the industry insider term for counting the dies, show that the layout is about 9×13 chips on the wafer. Equally advanced math says that the dies are about 33mm x 21mm or a hair under 700mm^2 for the entire thing. Please recall that this chip is a technology demo and is not optimized, the next generation will shrink a lot. On a similar 32nm process the single core Penwell is about 82mm^2, but that is a full SoC including a GPU.

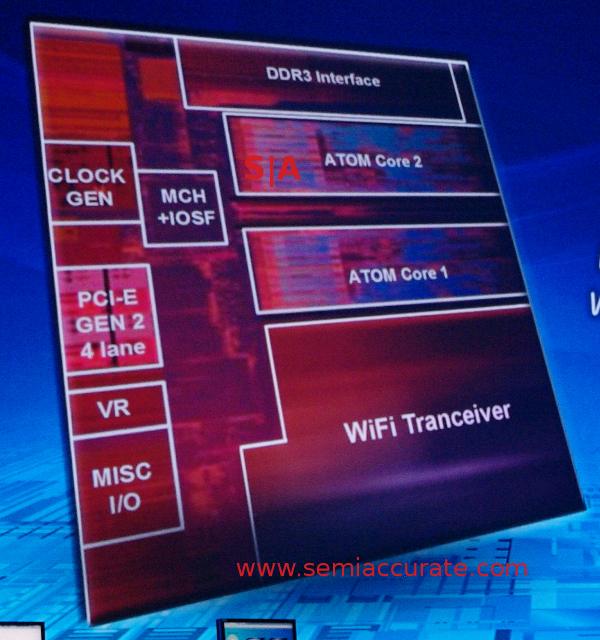

Diagram of the not small Rosepoint

Even if you doubled Penwell, GPU and all, you would only be a bit more than 25% of Rosepoint’s die size. Rosepoint does not have a GPU either, and that takes up a large chunk of Penwell’s die area. Short story, the radio is not small, really really not small. Then again, no one else can do it at all, so by that measure, it is infinitely smaller than the competition. Better yet for Intel, it will shrink in half on the next generation, the competition won’t.S|A

Charlie Demerjian

Latest posts by Charlie Demerjian (see all)

- What is Qualcomm’s Purwa/X Pro SoC? - Apr 19, 2024

- Intel Announces their NXE: 5000 High NA EUV Tool - Apr 18, 2024

- AMD outs MI300 plans… sort of - Apr 11, 2024

- Qualcomm is planning a lot of Nuvia/X-Elite announcements - Mar 25, 2024

- Why is there an Altera FPGA on QTS Birch Stream boards? - Mar 12, 2024