Last week Intel released their Stratix 10 FPGA after the world’s longest chip validation program. Remember when (then) Altera told SemiAccurate that this part would tape out in Q4/2014?

Last week Intel released their Stratix 10 FPGA after the world’s longest chip validation program. Remember when (then) Altera told SemiAccurate that this part would tape out in Q4/2014?

Here we are in the waning days of 2019 and The Stratix 10 makes it’s triumphant release on Intel’s 14nm process, ironically one of the better Intel Custom Foundry customer outcomes. Assuming that it did tape out on or around Q4/2014, first silicon probably took another quarter to come back, and lets just toss in two more quarters of random delays as well. That means it was a mere 4 years of validation, I guess Intel had a lot of learning to do on the non-CPU validation front. Or…

…Or things were broken, badly broken, on the Intel process side. Or Intel was having lots of meetings about how to spin the fact that these Stratix 10 FPGAs are based around four ARM A53 cores, something that conveniently wasn’t messaged this time around. Curious that. Any guesses which one it is, validation learning curves, broken process, or ARM cores? No points if you picked broken process, it is pretty obvious.

What is interesting is not the fact that a current Intel/Altera chip is broken, see anything 10nm for a PhD-level treatise on that topic, what is interesting is which bits that were broken this time around, basically the SerDes, plus the comical lengths Intel went to paper it over. Then hide the fact that they did. What are we talking about?

Much of those four years were spent because Intel’s 14nm process isn’t very good for analog and their 10nm is far less good to the point of being, well, you figure it out. Luckily for Intel the main place this showed up was in the SerDes on the external tiles. There are, now, four flavors of SerDes available for the Stratix 10, 17Gbps, 28Gbps, 58Gbps, and 112Gbps. The 17G parts kinda sorta trickled out a bit earlier and they were OK.

Then there was a delay for the 28G bearing Stratixes (Strati?). Why? Well it seems that there was an issue making them so Altera/Intel basically took their mid-range FPGAs that were made at TSMC, and worked just fine for reasons that officially probably have nothing to do with process, and cut out everything but the SerDes. They then slapped an EMIB interface on the parts and voila, working 28G SerDes.

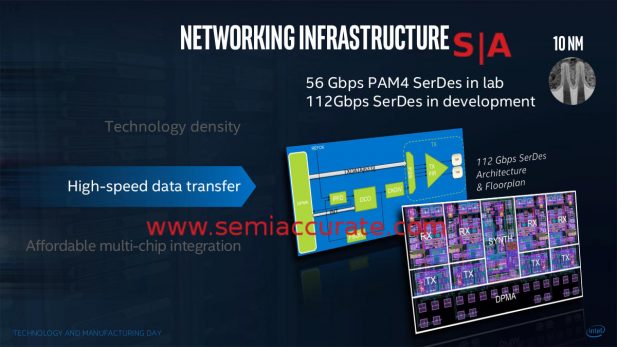

If that sounds harsh, look at the next two tiles, the 58G and 112G, both made at Intel on their famed 10nm process. They said so directly at Manufacturing Day in 2017, you know the one where they said 10nm was in great shape, yields were excellent, and volume was ramping hard. We laughed at the claims even if no one else did. That said, see the slide which clearly says 58G and 112G were built on Intel 10nm.

Here you go, official slides

It even goes as far as saying that the 58G SerDes is “in lab”, something they probably wanted you to take as, “it works” which it didn’t. If you were cynical you would say they were trying to mislead the audience. Why do we say this? Since that SerDes didn’t actually work, Intel paid Broadcom $50 million to take their 58G SerDes, which actually did work probably it wasn’t made at Intel, and spin it with EMIB pads. Take that device, slap an Intel sticker on it, scrub all refrences to 10nm and Intel fabs from future presentations, then claim victory. If you are buying a Stratix 10, make sure you get one with the E-Tile 58G SerDes, it is the working one.

Why do we make this distinction? In December Intel showed off their 112G SerDes at Architecture Day and it looked good. If you want a world class SerDes, just get the 58G variant and call it good, right? Not so fast, there is now an Intel variant of the 58G along with the 112G, both fabbed at Intel and both presumably on 10nm. These are called F-Tile and, well, consider yourself warned.

So with this SerDes debacle looking like it is getting close to over. Intel promised products to several customers that SemiAccurate talked to… last quarter. It is now this quarter and the 114nm FPGAs are ‘out’ likely because they promised the 10nm Agilex parts to customers next quarter. It would not go over well if Intel shipped their 10nm FPGAs before their 2014/2015 era 14nm FPGAs got out the door now would it?

All in all the whole Stratix 10 saga is finally coming to a close, four+ years later than planned, one quarter or so before it is utterly obsoleted by the 10nm parts. We will wait for you to catch your breath after you stop laughing, we don’t think it will actually ship on time either. Intel still isn’t admitting the heart of this chip is four ARM A53 cores, the one decent SerDes tile is made by Broadcom, and likely much more. To end on a positive note, at least this whole saga was fun to watch from the outside.S|A

Charlie Demerjian

Latest posts by Charlie Demerjian (see all)

- Qualcomm Is Cheating On Their Snapdragon X Elite/Pro Benchmarks - Apr 24, 2024

- What is Qualcomm’s Purwa/X Pro SoC? - Apr 19, 2024

- Intel Announces their NXE: 5000 High NA EUV Tool - Apr 18, 2024

- AMD outs MI300 plans… sort of - Apr 11, 2024

- Qualcomm is planning a lot of Nuvia/X-Elite announcements - Mar 25, 2024