During the IEDM conference in Washington, D.C. earlier today Fujitsu presented a paper jointly authored by SuVolta. The paper describes how a newly developed transistor with a deeply depleted channel can achieve the same power savings as those announced by Intel that has launched a FinFET-transistor, which the company calls a 3D transistor.

From a customer point of view the most important difference is that the Intel transistor requires the same threshold voltage across all transistors, whereas it can be varied using the SuVolta planar transistor. Multiple threshold voltages are often required when fabbing SoC’s and are therefore more suitable for foundries than the FinFET implementation. Also, implementation of FinFET’s outside the domain of Intel are several years away and is not expected until Foundries reach the 14nm node.

From a manufacturing point of view it is much simpler to fab the planar transistor as it is fabbed in a conventional CMOS process using bulk CMOS without the need for tricks like SiGe to strain the silicon.

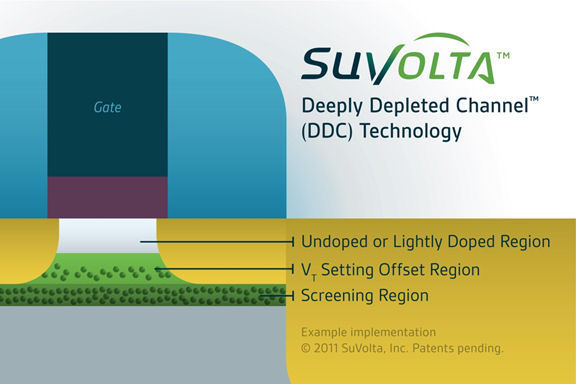

In the illustration below you can see the actual detail of a single transistor and the various layers in the transistor.

So far SuVolta has fabbed the transistor in 65nm and made all the results publicly available, but also claims that the technology scales to 32nm and beyond, but have yet to publish any of those findings.S|A

Updated: December 8, 2011 12pm. Correction to location of IEDM conference.

Mads Ølholm

Latest posts by Mads Ølholm (see all)

- Samsung shows off 20nm PRAM - Feb 28, 2012

- DDR4 shows up in the wild - Feb 28, 2012

- SanDisk develops the world’s smallest 128Gb flash chip - Feb 22, 2012

- Aussies create single atom transistor with precise control - Feb 21, 2012

- Chinese 16 core CPU uses message passing - Feb 21, 2012